**OPA817** JAJSMI7A – JULY 2022 – REVISED DECEMBER 2022

# OPA817 800MHz、高精度、ユニティ・ゲイン安定、FET 入力オペアンプ

## 1 特長

- 広い帯域幅:

- ゲイン帯域幅積:400MHz

- 帯域幅 (G = 1V/V):800MHz

- 大信号帯域幅 (2V<sub>PP</sub>):250MHz

- スルーレート: 1000V/μs

- 高精度

- 入力オフセット電圧:250µV (最大値)

- Aカオフセット電圧ドリフト:3.5µV/℃ (最大値)

- 入力電圧ノイズ:4.5nV/√Hz

- 入力バイアス電流:2pA

- 低歪み (R<sub>L</sub> = 100Ω、V<sub>O</sub> = 2V<sub>PP</sub>):

- 10MHz ੴ HD2、HD3:-86dBc、-100dBc

- 電源電圧範囲:6V~12.6V

- 消費電流:23.5mA

- シャットダウン電流:55µA

- OPA656 の性能アップグレード版

# 2 アプリケーション

- 高速データ・アクイジション (DAQ)

- アクティブ・プローブ

- オシロスコープ

- 広帯域のトランスインピーダンス・アンプ (TIA)

- ウェハー・スキャン機器

- 光通信モジュール

- 光時間領域反射測定法 (OTDR)

- テストおよび測定機器のフロントエンド

- 医療用および化学用分析器

#### 3 概要

OPA817 は、高速、高精度、広いダイナミック・レンジのア プリケーションに適した、ユニティ・ゲイン安定の電圧帰還 型オペアンプです。

OPA817 は、低ノイズの接合ゲート電界効果トランジスタ (JFET) 入力段を備えており、400MHz の広いゲイン帯域 幅と 6V~12.6V の電源電圧範囲を特長としています。 1000V/us の高いスルーレートにより、高速デジタイザ、ア クティブ・プローブ、その他のテストおよび測定アプリケー ションで高インピーダンスのバッファとして使用する場合、 広い大信号帯域幅と低歪みを実現できます。

OPA817 は、入力オフセット電圧が ±250µV と非常に低 く、オフセット電圧ドリフトは ±3.5µV/℃です。 入力バイアス 電流がピコアンペア単位であり、また、入力電圧ノイズが 低い (4.5nV/√Hz) ため、OPA817 は光学テスト機器、通 信機器、医療用および科学用計測機器に理想的な広帯 域トランスインピーダンス・アンプです。

OPA817 は、放熱用の露出サーマル・パッドが付いた 8 リ ードの WSON パッケージで供給されます。このデバイス は、産業用温度範囲の -40℃~+105℃で動作が規定さ れています。

#### パッケージ情報 <sup>(1)(2)</sup>

| 部品番号 |        | パッケージ         | 本体サイズ (公称)      |  |  |

|------|--------|---------------|-----------------|--|--|

|      | OPA817 | DTK (WSON, 8) | 3.00mm × 3.00mm |  |  |

- 利用可能なパッケージについては、データシートの末尾にあるパ ッケージ・オプションについての付録を参照してください。

- (2)デバイス比較表を参照してください。

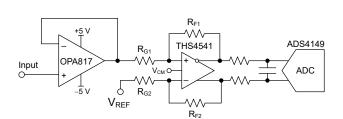

入力インピーダンスの高いデジタイザ用フロントエン ド

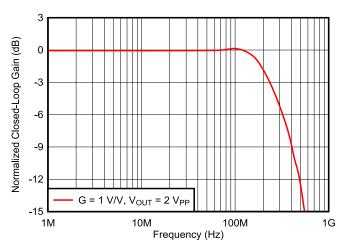

大信号周波数応答

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 、www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

## **Table of Contents**

| 1 特長                                                  | 1 | 9 Application and Implementation               | 17                      |

|-------------------------------------------------------|---|------------------------------------------------|-------------------------|

| 2 アプリケーション                                            |   | 9.1 Application Information                    | 17                      |

| 3 概要                                                  |   | 9.2 Typical Applications                       | 18                      |

| 4 Revision History                                    |   | 10 Power Supply Recommendations                | 19                      |

| 5 Device Comparison Table                             |   | 11 Layout                                      | 19                      |

| 6 Pin Configuration and Functions                     |   | 11.1 Layout Guidelines                         | 19                      |

| 7 Specifications                                      |   | 11.2 Layout Example                            | 21                      |

| 7.1 Absolute Maximum Ratings                          |   | 12 Device and Documentation Support            |                         |

| 7.2 ESD Ratings                                       |   | 12.1 Device Support                            | 22                      |

| 7.3 Recommended Operating Conditions                  |   | 12.2 Documentation Support                     | <mark>22</mark>         |

| 7.4 Thermal Information                               |   | 12.3 Receiving Notification of Documentation L | Jpdates <mark>22</mark> |

| 7.5 Electrical Characteristics: V <sub>S</sub> = ±5 V |   | <b>12.4</b> サポート・リソース                          | <u>22</u>               |

| 7.6 Typical Characteristics: V <sub>S</sub> = ±5 V    |   | 12.5 Trademarks                                | 22                      |

| 8 Detailed Description                                |   | 12.6 Electrostatic Discharge Caution           | 22                      |

| 8.1 Overview                                          |   | 12.7 Glossary                                  | 22                      |

| 8.2 Functional Block Diagram                          |   | 13 Mechanical, Packaging, and Orderable        |                         |

| 8.3 Feature Description                               |   | Information                                    | <mark>22</mark>         |

| ·                                                     |   |                                                |                         |

|                                                       |   |                                                |                         |

# **4 Revision History**

| CI | hanges from Revision * (July 2022) to Revision A (December 2022) | Pag |

|----|------------------------------------------------------------------|-----|

| •  | データシートのステータスを「事前情報」から <i>「量産データ」に変更</i>                          |     |

# **5 Device Comparison Table**

| DEVICE  | Supply Voltage (V) | BW (MHz) | Input | SLEW RATE (V/µs) | VOLTAGE NOISE (nV/√Hz) | MINIMUM STABLE<br>GAIN (V/V) |

|---------|--------------------|----------|-------|------------------|------------------------|------------------------------|

| OPA817  | ±6.3               | 400      | FET   | 1000             | 4.5                    | 1                            |

| OPA818  | ±6.5               | 2700     | FET   | 1400             | 2.2                    | 7                            |

| OPA657  | ±5                 | 1600     | FET   | 700              | 4.8                    | 7                            |

| OPA656  | ±5                 | 230      | FET   | 290              | 7                      | 1                            |

| OPA659  | ±6                 | 350      | FET   | 2550             | 8.9                    | 1                            |

| OPA858  | ±2.5               | 5500     | CMOS  | 2000             | 2.5                    | 7                            |

| THS4631 | ±15                | 210      | FET   | 1000             | 7                      | 1                            |

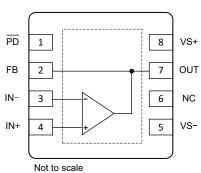

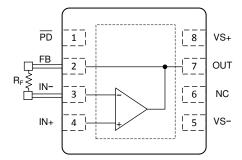

# **6 Pin Configuration and Functions**

NC - no internal connection

図 6-1. DTK Package, 8-Pin WSON With Thermal Pad (Top View)

表 6-1. Pin Functions

| PIN           |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                         |  |  |

|---------------|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.   |                     | DESCRIPTION                                                                                                                                                                                                         |  |  |

| FB            | 2     | 0                   | Feedback resistor connection (optional)                                                                                                                                                                             |  |  |

| IN-           | 3     | I                   | Inverting input                                                                                                                                                                                                     |  |  |

| IN+ 4 I       |       | I                   | Noninverting input                                                                                                                                                                                                  |  |  |

| NC 6 -        |       | _                   | o connect (no internal connection to die)                                                                                                                                                                           |  |  |

| OUT           | 7     | 0                   | Output of amplifier                                                                                                                                                                                                 |  |  |

| PD            | 1     | I                   | Power down (low = amplifier enabled, high = amplifier disabled); internal 2-M $\Omega$ pull-up allows floating this pin                                                                                             |  |  |

| VS-           | 5     | Р                   | Negative power supply                                                                                                                                                                                               |  |  |

| VS+           | VS+ 8 |                     | Positive power supply                                                                                                                                                                                               |  |  |

| Thermal pad — |       | _                   | Electrically isolated from the die substrate. The thermal pad can be connected to any potential between the device power-supplies, but it is recommended to connect it to a heat-spreading plane, typically ground. |  |  |

(1) I = input, O = output, P = power

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                                            | MIN MA                  | ٩X  | UNIT |

|------------------|----------------------------------------------------------------------------|-------------------------|-----|------|

| Vs               | Total supply voltage (V <sub>S+</sub> - V <sub>S-</sub> )                  |                         | 13  | V    |

|                  | Maximum dV <sub>S</sub> /dT for supply turn-on and turn-off <sup>(2)</sup> |                         | 1   | V/µs |

| VI               | Input voltage                                                              | V <sub>S-</sub>         | 'S+ | V    |

| V <sub>ID</sub>  | Differential input voltage                                                 | ±                       | Vs  | V    |

| I <sub>I</sub>   | Continuous input current                                                   | ±                       | 10  | mA   |

| Io               | Continuous output current <sup>(3)</sup>                                   | ±                       | 30  | mA   |

|                  | Continuous power dissipation                                               | See Thermal Information | n   |      |

| TJ               | Maximum junction temperature                                               | 1                       | 50  | °C   |

| T <sub>A</sub>   | Operating free-air temperature                                             | -40 1                   | 05  | °C   |

| T <sub>stg</sub> | Storage temperature                                                        | <b>–</b> 65 1           | 25  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) Staying below this specification ensures that the edge-triggered ESD absorption devices across the supply pins remain off

- (3) Long-term continuous current for electromigration limits.

#### 7.2 ESD Ratings

|                    |               |                                                                       | VALUE | UNIT |

|--------------------|---------------|-----------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 |      |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1500 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                   |                      | MIN | NOM | MAX  | UNIT |

|-----------------------------------|----------------------|-----|-----|------|------|

| V <sub>S+</sub> - V <sub>S-</sub> | Total supply voltage | 6   | 10  | 12.6 | V    |

| T <sub>A</sub>                    | Ambient temperature  | -40 | 25  | 105  | °C   |

#### 7.4 Thermal Information

|                       |                                              | OPA817     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DTK (WSON) | UNIT |

|                       |                                              | 8 PINS     |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 64.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 53.0       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 32.8       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.3        | °C/W |

| $Y_{JB}$              | Junction-to-board characterization parameter | 32.8       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 9.0        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Submit Document Feedback

# 7.5 Electrical Characteristics: $V_S = \pm 5 V$

| unless                          | otherwise noted)                   |                                                                                                              |     |            |       |            |

|---------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|------------|-------|------------|

|                                 | PARAMETER                          | TEST CONDITIONS                                                                                              | MIN | TYP        | MAX   | UNIT       |

| AC PER                          | FORMANCE                           |                                                                                                              |     |            |       |            |

|                                 |                                    | $V_{OUT} = 200 \text{ mV}_{PP}$                                                                              |     | 800        |       |            |

| SSBW                            | Small-signal bandwidth             | $V_{OUT}$ = 200 m $V_{PP}$ , G = 2 V/V                                                                       |     | 400        |       | MHz        |

| OODVV                           | Smail-signal bandwidth             | $V_{OUT} = 200 \text{ mV}_{PP}, G = 5 \text{ V/V}$                                                           |     | 100        |       | IVII IZ    |

|                                 |                                    | V <sub>OUT</sub> = 200 mV <sub>PP</sub> , G = 10 V/V                                                         |     | 40         |       |            |

| GBWP                            | Gain-bandwidth product             | V <sub>OUT</sub> = 200 mV <sub>PP</sub> , G = 100 V/V                                                        |     | 400        |       | MHz        |

| LCDW                            | Lorge signal handwidth             | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                                         |     | 250        |       | NAL I-     |

| LSBW                            | Large-signal bandwidth             | V <sub>OUT</sub> = 4 V <sub>PP</sub>                                                                         |     | 140        |       | MHz        |

|                                 | Bandwidth for 0.1-dB flatness      | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                                         |     | 100        |       | MHz        |

| 0.0                             | Slew rate (10% to 90%)             | V <sub>OUT</sub> = 4–V step                                                                                  |     | 1000       |       |            |

| SR                              | Slew rate (10% to 90%)             | V <sub>OUT</sub> = 1–V step, Gain = 2 V/V                                                                    |     | 750        |       | V/µs       |

| t <sub>R</sub> , t <sub>F</sub> | Rise, fall time                    | V <sub>OUT</sub> = 200-mV step                                                                               |     | 0.7        |       | ns         |

|                                 | Settling time to 0.1%,             | V <sub>OUT</sub> = 2–V step                                                                                  |     | 6          |       | ns         |

|                                 | Overshoot and undershoot           | V <sub>OUT</sub> = 2–V step                                                                                  |     | 8          |       | %          |

|                                 | Output Overdrive recovery time     | $V_{OUT} = V_{S-}$ to $V_{S+}$ , $G = 2 \text{ V/V}$ ,                                                       |     | 15         |       | ns         |

|                                 |                                    | f = 1 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                              |     | -110       |       |            |

|                                 | Second-order harmonic distortion   | f = 10 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                             |     | -86        |       | dBc        |

| HD2                             |                                    | f = 50 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                             |     | <b>–76</b> |       |            |

|                                 |                                    | $f = 10 \text{ MHz}, V_{OUT} = 2 V_{PP}, R_L = 1 \text{ k}\Omega$                                            |     | <b>–97</b> |       |            |

|                                 |                                    | f = 1 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                              |     | -120       |       |            |

|                                 | Third-order harmonic distortion    | f = 10 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                             |     | -100       |       |            |

| HD3                             |                                    | f = 50 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                             |     | <u>–68</u> |       | dBc        |

|                                 |                                    | $f = 10 \text{ MHz}, V_{OUT} = 2 V_{PP}, R_L = 1 k\Omega$                                                    |     | -102       |       |            |

|                                 | Input voltage noise                | f ≥ 200 kHz                                                                                                  |     | 4.5        |       | nV/√Hz     |

| e <sub>N</sub>                  | Voltage noise 1/f corner frequency | 1 - 200 M 12                                                                                                 |     | 2.6        |       | kHz        |

|                                 | Input current noise                |                                                                                                              |     | 18         |       | fA/√Hz     |

| DC PER                          | FORMANCE                           |                                                                                                              |     |            |       | 17-7 11 12 |

| DO I EI                         | ONWARDE                            | V <sub>OUT</sub> = ±1 V                                                                                      | 78  | 85         |       |            |

| ٨                               | Open leep veltege gein             | $T_A = -40^{\circ} \text{C to } +85^{\circ} \text{C}$                                                        | 70  |            |       | dB         |

| A <sub>OL</sub>                 | Open-loop voltage gain             | $T_A = -40^{\circ} \text{C to } +05^{\circ} \text{C}$ $T_A = -40^{\circ} \text{C to } +105^{\circ} \text{C}$ | 69  |            |       | uБ         |

|                                 |                                    | 1440 C to +103 C                                                                                             | 09  | 50         | +250  |            |

| . ,                             | lament referred affect veltaria    | T = 40°C to 105°C                                                                                            |     | 50         | ±250  | /          |

| V <sub>OS</sub>                 | Input-referred offset voltage      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          |     |            | ±500  | μV         |

|                                 |                                    | $T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$                                                         |     |            | ±600  |            |

|                                 | Input offset voltage drift         | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          |     | 1          | ±3.5  | μV/°C      |

|                                 |                                    | $T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$                                                         |     | 1          | ±3.5  |            |

|                                 |                                    |                                                                                                              |     | 2          | ±20   | _          |

| l <sub>B</sub>                  | Input bias current                 | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          |     |            | ±1000 | pA         |

|                                 |                                    | $T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$                                                         |     |            | ±1500 |            |

|                                 |                                    |                                                                                                              |     | 1          | ±20   |            |

| los                             | Input offset current               | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          |     |            | ±500  | pA         |

|                                 |                                    | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                                                               |     |            | ±750  |            |

|                                 | Internal feedback trace resistance | Device turned OFF, OUT to FB pin resistance                                                                  |     | 0.7        |       | Ω          |

# 7.5 Electrical Characteristics: $V_S = \pm 5 V$ (continued)

|                 | PARAMETER                                  | TEST CONDITIONS                                                             | MIN | TYP       | MAX  | UNIT     |

|-----------------|--------------------------------------------|-----------------------------------------------------------------------------|-----|-----------|------|----------|

| INPUT           |                                            |                                                                             |     |           |      |          |

|                 |                                            |                                                                             | 2.1 | 2.7       |      |          |

|                 | Most positive input voltage <sup>(1)</sup> | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               | 2.0 |           |      | V        |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                              | 2.0 |           |      |          |

|                 |                                            |                                                                             |     | -3.9      | -3.5 |          |

|                 | Most negative input voltage <sup>(1)</sup> | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               |     |           | -3.4 | V        |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                              |     |           | -3.4 |          |

|                 |                                            | V <sub>CM</sub> = ±0.5 V                                                    | 84  | 110       |      |          |

| CMRR            | Common-mode rejection ratio                | T <sub>A</sub> = -40°C to 85°C                                              | 83  |           |      | dB       |

|                 |                                            | T <sub>A</sub> = -40°C to 105°C                                             | 82  |           |      |          |

|                 | Input impedance common-mode                |                                                                             |     | 60    2.9 |      | GΩ    pF |

|                 | Input capacitance differential mode        |                                                                             |     | 0.1       |      | pF       |

| OUTPU           | г                                          |                                                                             |     |           |      |          |

|                 |                                            | no-load                                                                     |     | -3.9      | -3.6 |          |

| .,              | Output voltage, low                        | R <sub>L</sub> = 100 Ω                                                      |     | -3.7      | -3.4 | V        |

| $V_{OL}$        |                                            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               |     |           | -3.3 |          |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                              |     |           | -3.2 |          |

|                 | Output voltage, high                       | no-load                                                                     | 3.7 | 3.9       |      |          |

|                 |                                            | R <sub>L</sub> = 100 Ω                                                      | 3.4 | 3.7       |      |          |

| V <sub>OH</sub> |                                            | $T_A = -40$ °C to +85°C                                                     | 3.3 |           |      | V        |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C,$                             | 3.2 |           |      |          |

|                 |                                            | $V_{OUT} = \pm 1 \text{ V}, \Delta V_{OS} < 2 \text{ mV}$                   | ±58 | 80        |      |          |

|                 | Linear output drive (sourcing/sinking)     | $T_A = -40 \text{ to } 85^{\circ}\text{C}, \ \Delta V_{OS} < 3 \text{ mV}$  | ±40 |           |      | mA       |

|                 |                                            | $T_A = -40 \text{ to } 105^{\circ}\text{C}, \ \Delta V_{OS} < 3 \text{ mV}$ | ±35 |           |      |          |

|                 | Short-circuit current                      |                                                                             |     | ±100      |      | mA       |

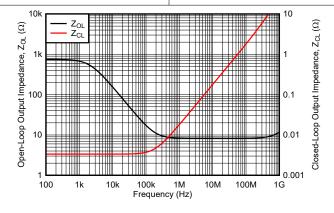

| Z <sub>O</sub>  | Closed loop output Impedance               | f = 100 kHz                                                                 |     | 0.04      |      | Ω        |

| POWER           | SUPPLY                                     |                                                                             |     |           |      |          |

|                 |                                            |                                                                             |     | 23.5      | 24.5 |          |

| $I_Q$           | Quiescent current                          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               |     |           | 24.7 | mA       |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                              |     |           | 24.9 |          |

|                 |                                            | $\Delta V_{S+} = \pm 0.5 \text{ V}$                                         | 80  | 100       |      |          |

| PSRR+           | Power-supply rejection ratio               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               | 77  |           |      | dB       |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                              | 76  |           |      |          |

|                 |                                            | $\Delta V_{S-} = \pm 0.5 \text{ V},$                                        | 80  | 100       |      |          |

| PSRR-           | Power-supply rejection ratio               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               | 77  |           |      | dB       |

|                 |                                            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                              | 76  |           |      |          |

# 7.5 Electrical Characteristics: $V_S = \pm 5 V$ (continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                | PARAMETER                                  | TEST CONDITIONS                                                                                      | MIN | TYP | MAX | UNIT |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| POWER DOWN         Enable voltage threshold       Specified on above $(V_{S+}) - 1 V$ 4       V         Disable voltage threshold       Specified off below $(V_{S+}) - 3 V$ 2       V         Power-down quiescent current $\overline{PD} \le (V_{S+}) - 3 V$ 55       100       uA         Power-down pin bias current in shutdown mode $\overline{PD} = 0 V \text{ to } (V_{S+}) - 3 V$ 9       12       uA |                                            |                                                                                                      |     |     |     |      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Enable voltage threshold                   | Specified on above (V <sub>S+</sub> ) – 1 V                                                          |     |     | 4   | V    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Disable voltage threshold                  | Specified off below (V <sub>S+</sub> ) – 3 V                                                         | 2   |     |     | V    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Power-down quiescent current               | $\overline{PD} \le (V_{S+}) - 3V$                                                                    |     | 55  | 100 | uA   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | ·                                          | PD = 0 V to (V <sub>S+</sub> ) – 3 V                                                                 |     | 9   | 12  | uA   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Power-down pin bias current in active mode | $\overline{PD} = (V_{S+}) - 1 \text{ V to } (V_{S+})$                                                |     | 0.5 | 1   | uA   |  |  |  |

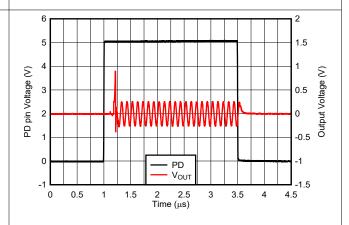

|                                                                                                                                                                                                                                                                                                                                                                                                                | Turn-on time delay                         | Time from $\overline{PD}$ voltage exceeds threshold to $V_{OUT}$ = 90% of final value, $V_{IN}$ = 1V |     | 0.3 |     | μs   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Turn-off time delay                        | Time from PD voltage reduces below threshold to $I_Q$ = 10% of active mode value                     |     | 0.1 |     | μs   |  |  |  |

<sup>(1)</sup> Input range for CMRR > 77-dB.

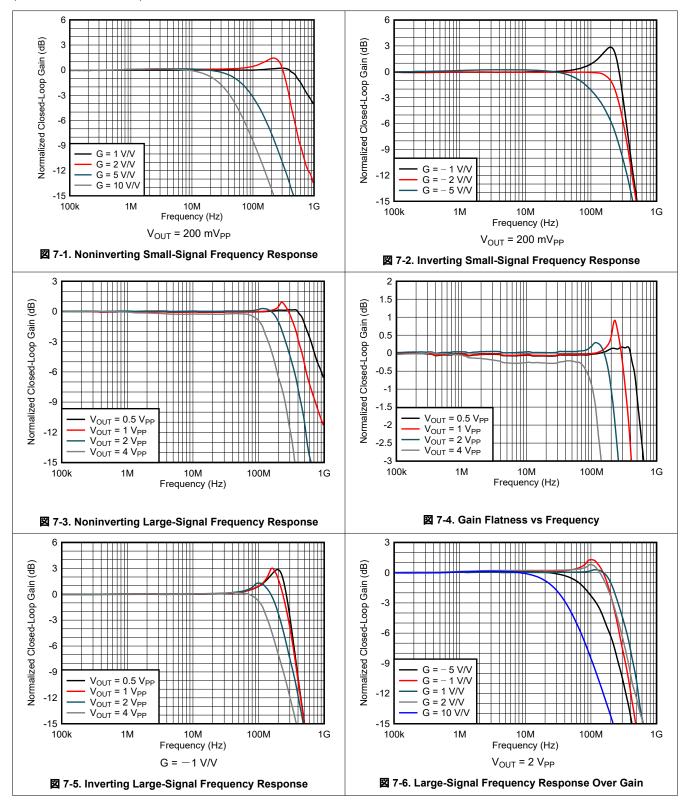

## 7.6 Typical Characteristics: $V_S = \pm 5 \text{ V}$

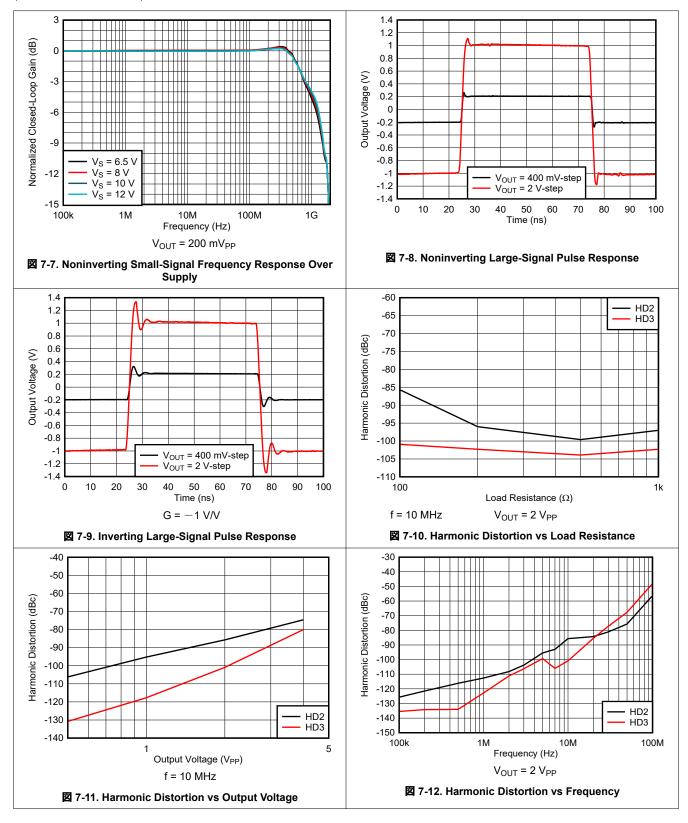

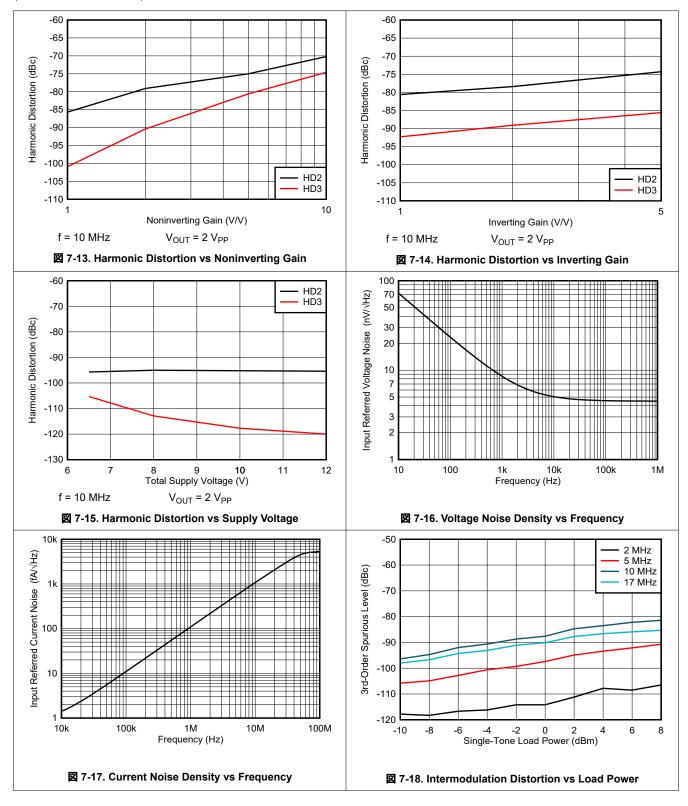

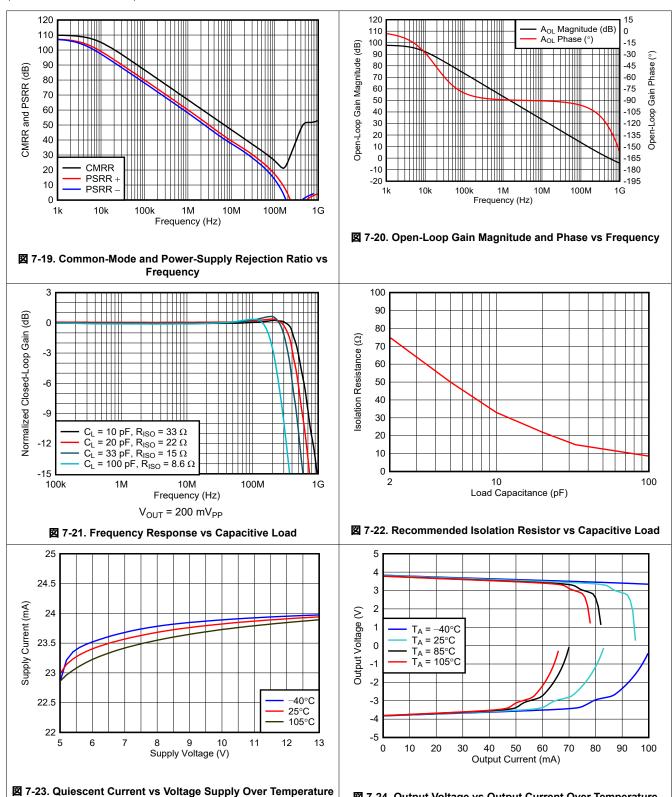

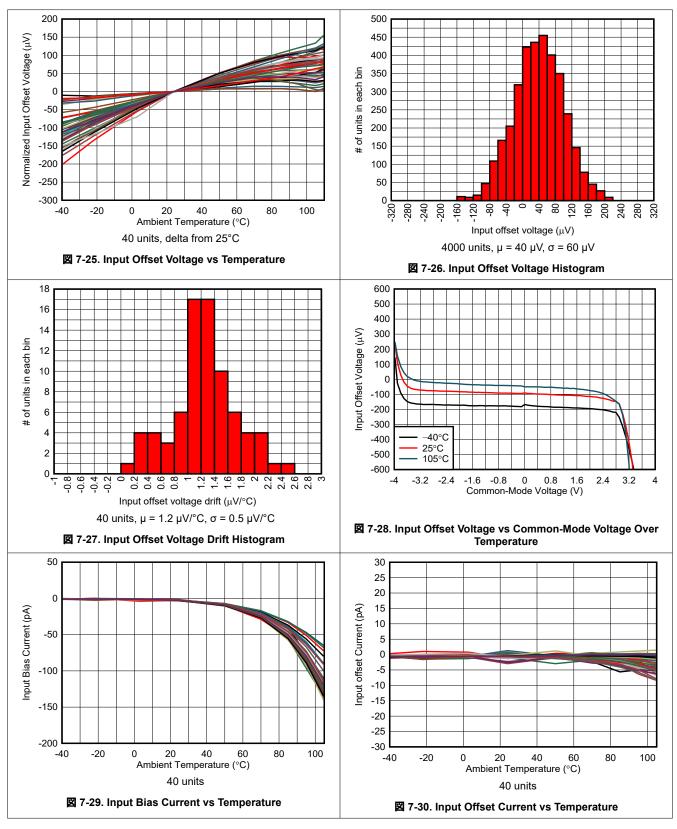

At G = 1 V/V,  $R_F$  = 0  $\Omega$ ,  $R_F$  = 250  $\Omega$  for other gains,  $R_L$  = 100  $\Omega$ , input and output referenced to mid-supply, and  $T_A \cong 25^{\circ}C$ (unless otherwise noted).

図 7-24. Output Voltage vs Output Current Over Temperature

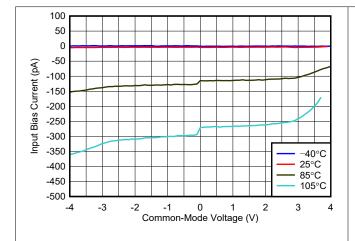

図 7-31. Input Bias Current vs Common-Mode Voltage Over Temperature

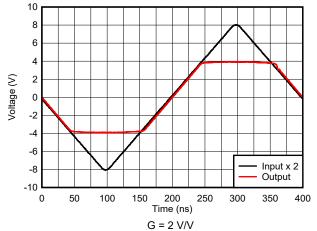

図 7-32. Noninverting Output Overdrive Recovery

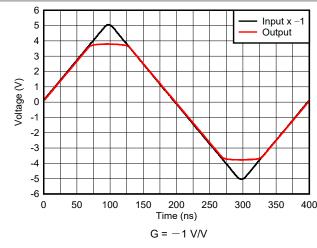

図 7-33. Inverting Output Overdrive Recovery

図 7-34. Turn-On and Turn-Off Waveform

図 7-35. Open-Loop and Closed-Loop Output Impedance vs Frequency

## 8 Detailed Description

#### 8.1 Overview

The OPA817 is a high voltage, unity gain stable, 400 MHz gain-bandwidth product (GBWP), voltage feedback operational amplifier (op amp) featuring a 4.5 nV/ $\sqrt{\text{Hz}}$  low noise JFET input stage. The low offset voltage (250  $\mu$ V maximum), offset voltage drift (3.5  $\mu$ V/ $^{\circ}$ C maximum), and unity gain bandwidth of 800 MHz makes it ideal for high input impedance, high-speed data acquisition front-ends. The high voltage capability combined with 1000 V/ $\mu$ s slew rate enables applications needing wide output swings (9 V<sub>PP</sub> at V<sub>S</sub> = 12 V) for high-frequency signals such as those often found in medical instrumentation, optical front-end, test, and measurement applications. The low noise JFET input with pico-amperes of bias current makes the device attractive in high-gain TIA applications and in test and measurement front-ends. OPA817 also features a power-down mode that disables the core amplifier for power savings.

The OPA817 is built using TI's proprietary high-voltage, high-speed, complementary bipolar SiGe process.

## 8.2 Functional Block Diagram

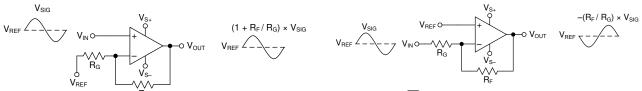

The OPA817 is a conventional voltage feedback op amp with two high-impedance inputs and a low-impedance output.  $\boxtimes$  8-1 and  $\boxtimes$  8-2 shows two standard amplifier configuration examples that are supported for this device. The reference voltage (V<sub>REF</sub>) level shifts the DC operating point for each configuration, which is typically set to mid-supply in single-supply operation. V<sub>REF</sub> is typically set to ground in split-supply applications.

図 8-1. Noninverting Amplifier

図 8-2. Inverting Amplifier

#### 8.3 Feature Description

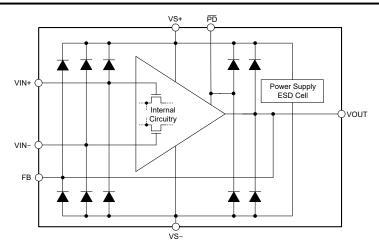

#### 8.3.1 Input and ESD Protection

The OPA817 is built using a very high-speed complementary bipolar process. The internal junction breakdown voltages are relatively low for these very small geometry devices. These breakdowns are reflected in the *Absolute Maximum Ratings*. As ☒ 8-3 shows, all device pins are protected with internal ESD protection diodes to the power supplies.

The diodes provide moderate protection to input overdrive voltages beyond the supplies as well. The protection diodes can typically support a 10-mA continuous current. Where higher currents are possible (for example, in systems with  $\pm 12$ -V supply parts driving into the OPA817), current limiting series resistors should be added in series with the two inputs to limit the current. Keep these resistor values as low as possible because high values degrade both noise performance and frequency response. There are no back-to-back ESD diodes between  $V_{IN+}$  and  $V_{IN-}$ . As a result, the differential input voltage between  $V_{IN+}$  and  $V_{IN-}$  is entirely absorbed by the  $V_{GS}$  of the input JFET differential pair and must not exceed the voltage ratings shown in the *Absolute Maximum Ratings*.

図 8-3. Internal ESD Protection

#### 8.3.2 Feedback Pin

For high speed analog design, minimizing parasitic capacitances and inductances is critical to get the best performance from a high-speed amplifier such as the OPA817. Parasitic capacitance and inductance are especially detrimental in the feedback path and at the inverting input. They result in undesired poles and zeroes in the feedback that could result in reduced phase margin or instability. Techniques used to correct this phase margin reduction often result in reduced application bandwidth. To keep system engineers from making these tradeoff choices and to simplify the PCB layout, OPA817 features an FB pin on the same side as the inverting input pin (IN–).  $\boxtimes$  8-4 shows how this feature allows for a very short feedback resistor (R<sub>F</sub>) connection between the FB and the IN– pin, which minimizes parasitic capacitance and inductance with minimal PCB design effort. Internally the FB pin is connected to OUT pin through metal routing on the silicon. Due to the fixed metal sizing of this connection, the FB pin has limited current carrying capability. Therefore, the specifications in the *Absolute Maximum Ratings* section must be adhered to for continuous operation. For applications requiring high accuracy, the metal routing resistance from OUT to FB can be considered and added to R<sub>F</sub> to set the desired gain. For more information, see  $2 7 \times 10^{-2}$  7.5.

図 8-4. R<sub>F</sub> Connection Between FB and IN- Pins

#### 8.3.3 FET-Input Architecture with Wide Gain-Bandwidth Product

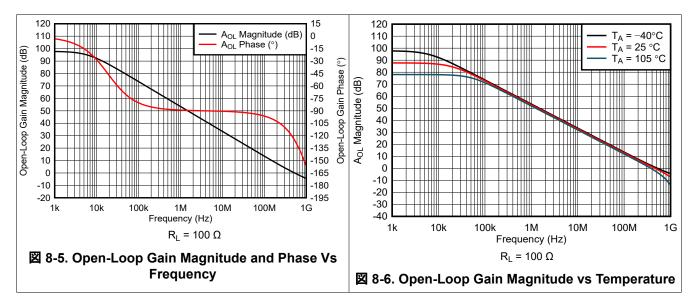

$\boxtimes$  8-5 shows the open-loop gain and phase response of the OPA817. The GBWP of an op amp is measured in the 20 dB/decade constant slope region of the A<sub>OL</sub> magnitude plot. The open-loop gain of 60 dB for the OPA817 is along this 20 dB/decade slope and the corresponding frequency intercept is at 400 kHz. Converting 60 dB to linear units (1000 V/V) and multiplying it with the 400 kHz frequency intercept gives the GBWP of OPA817 as 400 MHz. As can be inferred from the A<sub>OL</sub> Bode plot, the second pole in the A<sub>OL</sub> response occurs after A<sub>OL</sub> magnitude drops below 0 dB (1 V/V). This results in phase change of less than 180° at 0 dB A<sub>OL</sub> indicating that the amplifier will be stable in a gain of 1 V/V. Amplifiers like OPA817 that are JFET-input, low noise and unitygain stable can be used as high input impedance buffers and gain stages with minimal degradation in SNR. It has 800 MHz of SSBW in gain of 1V/V configuration with approximately 55° phase margin.

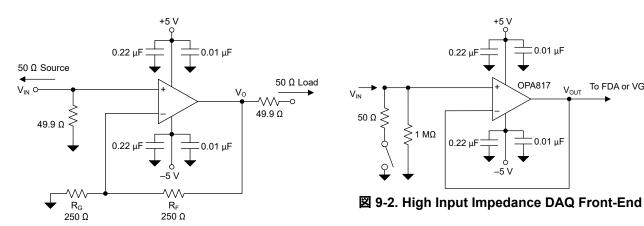

The low input offset voltage and offset voltage drift of OPA817 makes it a very suitable amplifier for high precision, high input impedance, wideband data acquisition system front-ends. As  $\boxtimes$  9-2 shows, the system benefits from the low noise JFET input stage with pico-amperes of input bias current to achieve higher precision at 1-M $\Omega$  input impedance settings and higher SNR at 50- $\Omega$  input impedance setting simultaneously in a typical data acquisition front-end circuit.

#### 8.3.4 Device Functional Modes

#### 8.3.4.1 Power-Down (PD) Pin

The OPA817 includes a power-down mode for low-power or standby operation and only consumes 55  $\mu$ A (typical) of current when placed in power-down mode. Low-power systems that are only active for small periods of time benefit from this feature. The OPA817 can transition from low-power mode to active-mode in 300 ns (typical). For power-down pin control thresholds, refer to  $\forall 2 \neq 2 \neq 7.5$ . An internal pull-up resistor of 2-M $\Omega$  provides a weak pull-up to  $V_{S+}$  if  $\overline{PD}$  is left unconnected. An external 1-nF capacitor to  $V_{S+}$  may be used to avoid external noise coupling and false triggering. If the power-down mode is not used in an application, then connect the  $\overline{PD}$  pin to  $V_{S+}$ .

# 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

#### 9.1 Application Information

#### 9.1.1 Wideband, High-Input Impedance DAQ Front-End

The OPA817 features a unique combination of high GBWP, low-input voltage noise, and the DC precision of a trimmed JFET-input stage to provide a high input impedance for a voltage-feedback amplifier.

9-2 shows how its very high GBWP of 400 MHz and high large signal bandwidth of 250 Mhz can be used to either deliver wide signal bandwidths at high gains or to extend the achievable bandwidth or gain in typical high-speed, high-input impedance data acquisition front-end applications. To achieve the full performance of the OPA817, careful attention to the printed circuit board (PCB) layout and component selection is required as discussed in the following sections of this data sheet. OPA817 also features a wider supply range thereby enabling a wider common-mode input range to support higher input signal swings.

$\boxtimes$  9-1 shows the noninverting gain of +2 V/V circuit used as the basis for most of the *Typical Characteristics*. Most of the curves were characterized using signal sources with 50- $\Omega$  driving impedance, and with measurement equipment presenting a 50- $\Omega$  load impedance. As  $\boxtimes$  9-1 shows, the 49.9- $\Omega$  shunt resistor at the V<sub>IN</sub> terminal matches the source impedance of the test generator, while the 49.9- $\Omega$  series resistor at the V<sub>O</sub> terminal provides a matching resistor for the measurement equipment load. Generally, data sheet voltage swing specifications are at the output pin (V<sub>O</sub> in  $\boxtimes$  9-1) while output power specifications are at the matched 50- $\Omega$  load. As shown in  $\boxtimes$  9-1, the total 100- $\Omega$  load at the output combined with the 250- $\Omega$  total feedback network load presents the OPA817 with an effective output load of 83.3  $\Omega$  for the circuit.

図 9-1. Noninverting G = +2 V/V Configuration and Test Circuit

Voltage-feedback operational amplifiers, unlike current feedback amplifiers, can use a wide range of resistor values to set their gain. As  $\boxtimes$  9-1 shows, the parallel combination of R<sub>F</sub> || R<sub>G</sub> should always be kept to a lower value to retain a controlled frequency response for the noninverting voltage amplifier. In the noninverting configuration, the parallel combination of R<sub>F</sub> || R<sub>G</sub> will form a pole with the parasitic input capacitance at the inverting node of the OPA817 (including layout parasitic capacitance). For best performance, this pole should be at a frequency greater than the closed loop bandwidth for the OPA817.

#### 9.2 Typical Applications

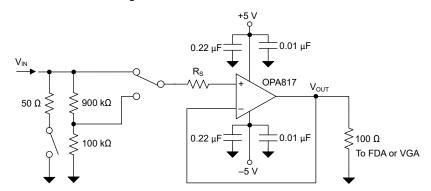

#### 9.2.1 High Input Impedance, 200 MHz, Digitizer Front-End Amplifier Design

The OPA817 offers a wide large-signal bandwidth, high-slew rate along with high-input impedance making it ideal for data acquisition systems. The trimmed DC precision of the OPA817 enables its use directly as front-end amplifier where low offset and offset voltage drift is needed.

図 9-3. High Input Impedance, 200 MHz, Digitizer Front-End Amplifier

#### 9.2.2 Design Requirements

表 9-1 lists the design requirements for a High Input Impedance, 200 MHz, Digitizer Front-End Amplifier.

| 20 ii 200igii itoquiioiiioite            |                                        |  |  |  |  |  |  |  |

|------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| Specification                            | Value                                  |  |  |  |  |  |  |  |

| Input Impedance                          | 1 ΜΩ / 50Ω                             |  |  |  |  |  |  |  |

| Input Range (1 MΩ / 50 Ω)                | 20 V <sub>PP</sub> / 2 V <sub>PP</sub> |  |  |  |  |  |  |  |

| Offset Drift                             | 3.5 μV/°C maximum                      |  |  |  |  |  |  |  |

| Noise at Highest Resolution (50 Ω Input) | 80 μV <sub>RMS</sub>                   |  |  |  |  |  |  |  |

表 9-1. Design Requirements

#### 9.2.3 Detailed Design Procedure

- Input Impedance: The JFET-input stage of the OPA817 offers giga ohm's of input impedance and therefore enables the front-end to be terminated with a 1 M $\Omega$  resistor while achieving excellent precision. A 50  $\Omega$  resistance can also be switched in offering matched termination for high-frequency signals. The OPA817 therefore enables the designer to use both 1 M $\Omega$  and 50  $\Omega$  termination in the same signal chain.

- Noise: The total noise of the front-end amplifier is the function of the voltage and current noise of the OPA817, input termination, and the resistors thermal noise. In 50 Ω mode, the dominant noise source, however, is contributed by the voltage noise of the OPA817 due to its presence across the complete bandwidth. Thus, the total RMS noise of the front-end amplifier shall be approximately equal to the voltage noise of OPA817 over 200 MHz.

The specified input referred voltage noise of the OPA817 is 4.5 nV/√Hz; for more information see セクション 7.5. The total integrated RMS noise at the input in a bandwidth of 200 MHz is given by the following equation:

$$En_{RMS} = 4.5 \text{ nV}/\sqrt{Hz} \times \sqrt{(200 \text{ MHz} \times 1.57)} = 80 \mu V_{RMS}.$$

(1)

The Brickwall correction factor of 1.57 is applied assuming the bandwidth will be limited to 200 MHz with a single pole RC-filter before digitizing the signal with the ADC. Detailed calculations can be found on TI Precision Labs – Op Amps: Noise – Spectral Density.

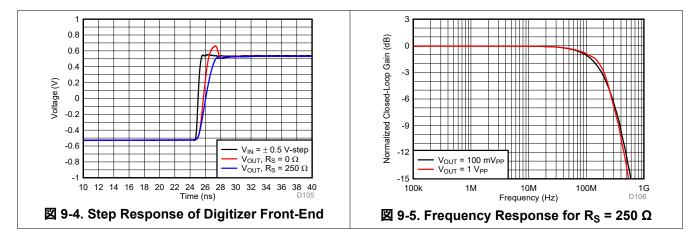

Optimizing Overshoot: The OPA817 features an internal slew-boost circuit to deliver fast rise-time in applications needing high slew rates such as when configured as a transimpedance amplifier. For applications where overshoot needs to be limited, the input slew rates can be limited with introducing a series resistance ( $R_S$ ) as shown in  $\boxtimes$  9-3. The resistance  $R_S$  forms a low pass filter with the input capacitance of approximately 2.6 pF at the noninverting pin of the OPA817 limiting the input slew rate to the amplifier. 🗵 9-4 shows how limiting the input slew rate to the amplifier results in good overshoot performance, and  $\boxtimes$  9-5 shows how this achieves a small signal and large signal bandwidth of 200 MHz.

#### 9.2.4 Application Curves

## 10 Power Supply Recommendations

The OPA817 is intended to operate on supplies ranging from 6 V to 12.6 V. OPA817 supports single-supply, split, balanced, and unbalanced bipolar supplies. When operating at supplies below 8 V, consideration must be given to the input common-mode range of the amplifier. Under these supply conditions, the common-mode must be biased appropriately for linear operation. Thus, the limit to lower supply voltage operation is the usable input voltage range for the JFET-input stage.

#### 11 Layout

#### 11.1 Layout Guidelines

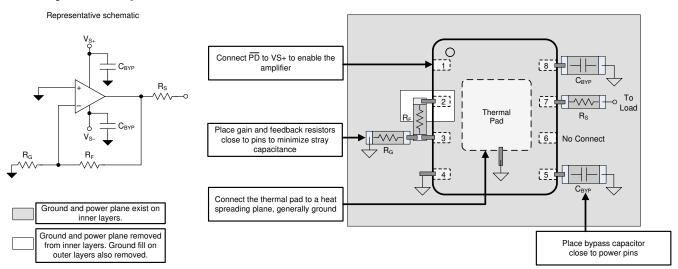

Achieving optimum performance with a high-frequency amplifier like the OPA817 requires careful attention to board layout parasitics and external component types. Recommendations that will optimize performance include the following:

1. Minimize parasitic capacitance to any ac ground for all of the signal I/O pins. Parasitic capacitance on the output and inverting input pins can cause instability. On the noninverting input, parasitic capacitance can react with the source impedance to cause unintentional bandlimiting. Ground and power metal planes act as one of the plates of a capacitor while the signal trace metal acts as the other separated by PCB dielectric. To reduce this unwanted capacitance, care must be taken to minimize the routing of the feedback network. A plane cutout around and underneath the inverting input pin on all ground and power planes is recommended. Otherwise, ground and power planes should be unbroken elsewhere on the board.

- 2. **Minimize the distance (less than 0.25-in) from the power-supply pins to high-frequency decoupling capacitors.** Use high quality, 100-pF to 0.1-μF, C0G and NPO-type decoupling capacitors with voltage ratings at least three times greater than the amplifiers maximum power supplies to ensure that there is a low-impedance path to the amplifiers power-supply pins across the amplifiers gain bandwidth specification. At the device pins, do not allow the ground and power plane layout to be in close proximity to the signal I/O pins. Avoid narrow power and ground traces to minimize inductance between the pins and the decoupling capacitors. Larger (2.2-μF to 6.8-μF) decoupling capacitors, effective at lower frequency, must be used on the supply pins. These can be placed further from the device and are shared among several devices in the same area of the PC board.

- 3. Careful selection and placement of external components will preserve the high frequency performance of the OPA817. Use low-reactance resistors. Surface-mount resistors work best and allow a tighter overall layout. Never use wirewound type resistors in a high frequency application. Because the output pin and inverting input pin are the most sensitive to parasitic capacitance, always position the feedback and series output resistor, if any, as close as possible to the inverting input and the output pin, respectively.

- Other network components, such as noninverting input termination resistors, should also be placed close to the package. Even with a low parasitic capacitance at the noninverting input, high external resistor values can create significant time constants that can degrade performance. When OPA817 is configured as a conventional voltage amplifier, keep the resistor values as low as possible and consistent with the load driving considerations. Decreasing the resistor values keeps the resistor noise terms low and minimizes the effect of the parasitic capacitance. However, lower resistor values increase the dynamic power consumption because  $R_{\rm F}$  and  $R_{\rm G}$  become part of the output load network of the amplifier.

- 4. **Heat dissipation is important for a high voltage device like OPA817**. For good thermal relief, the thermal pad should be connected to a heat spreading plane that is preferably on the same layer as OPA817 or connected by as many vias as possible, if the plane is on a different layer. It is recommended to have at least one heat spreading plane on the same layer as the OPA817 that makes a direct connection to the thermal pad with wide metal for good thermal conduction when operating at high ambient temperatures. If more than one heat spreading plane is available, then connect them by a number of vias to further improve the thermal conduction.

#### 11.1.1 Thermal Considerations

The OPA817 will not require heatsinking or airflow in most applications. Maximum allowed junction temperature will set the maximum allowed internal power dissipation as described in the following paragraph. In no case should the maximum junction temperature be allowed to exceed 150°C.

Operating junction temperature ( $T_J$ ) is given by  $T_A + P_D \times R_{\theta JA}$ . The total internal power dissipation ( $P_D$ ) is the sum of quiescent power ( $P_{DQ}$ ) and additional power dissipated in the output stage ( $P_{DL}$ ) to deliver load power. Quiescent power is the specified no-load supply current times the total supply voltage across the part.  $P_{DL}$  will depend on the required output signal and load, but for a grounded resistive load the  $P_{DL}$  will be at a maximum when the output is fixed at a voltage equal to 1/2 of either supply voltage (for balanced bipolar supplies). Under this condition  $P_{DL} = V_S^{-2}/(4 \times R_L)$  where  $R_L$  includes feedback network loading.

Note that it is the power in the output stage and not into the load that determines internal power dissipation.

As a worst-case example, compute the maximum  $T_J$  using OPA817 in the circuit of  $\boxtimes$  9-1 operating at the maximum specified ambient temperature of +105°C and driving a grounded 100- $\Omega$  load.

$$P_D = 10 \text{ V} \times 23.5 \text{ mA} + 5^2 / (4 \times (100 \Omega || 500 \Omega)) \approx 310 \text{ mW}$$

Maximum  $T_J = 105^{\circ}C + (0.310 \text{ W} \times 64.9^{\circ}C/\text{W}) = 125.1^{\circ}C.$

All actual applications will be operating at lower internal power and junction temperature.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

#### 11.2 Layout Example

図 11-1. Layout Recommendation

## 12 Device and Documentation Support

## 12.1 Device Support

#### 12.1.1 Development Support

• Texas Instruments, Wide Bandwidth Optical Front-end Reference Design

#### **12.2 Documentation Support**

#### 12.2.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, OPA817EVM User's Guide

- · Texas Instruments, Transimpedance Considerations for High-Speed Amplifiers application report

- Texas Instruments, Maximizing the Dynamic Range of Analog TIA Front-End techincal brief

- Texas Instruments, What You Need To Know About Transimpedance Amplifiers Part 1

- Texas Instruments, What You Need To Know About Transimpedance Amplifiers Part 2

- · Texas Instruments, Training Video: How to Design Transimpedance Amplifier Circuits

- Texas Instruments, Training Video: High-Speed Transimpedance Amplifier Design Flow

#### 12.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 12.5 Trademarks

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 12.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.7 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

#### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

www.ti.com 19-May-2023

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| OPA817DTKR       | ACTIVE        | WSON         | DTK                | 8    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 105   | 817                     | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Dec-2022

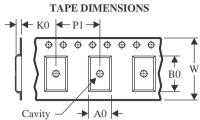

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

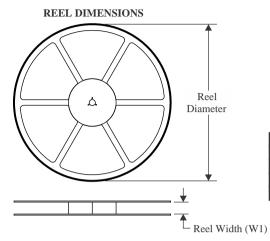

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA817DTKR | WSON            | DTK                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

PACKAGE MATERIALS INFORMATION

www.ti.com 17-Dec-2022

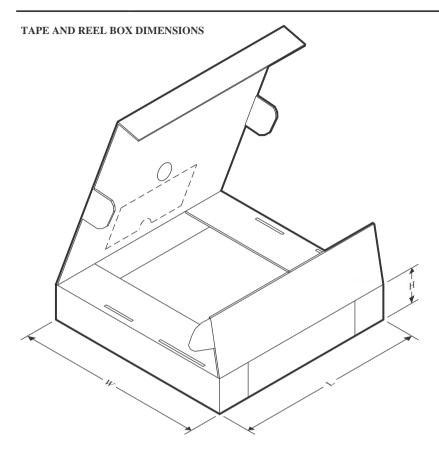

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| OPA817DTKR | WSON         | DTK             | 8    | 3000 | 367.0       | 367.0      | 35.0        |  |

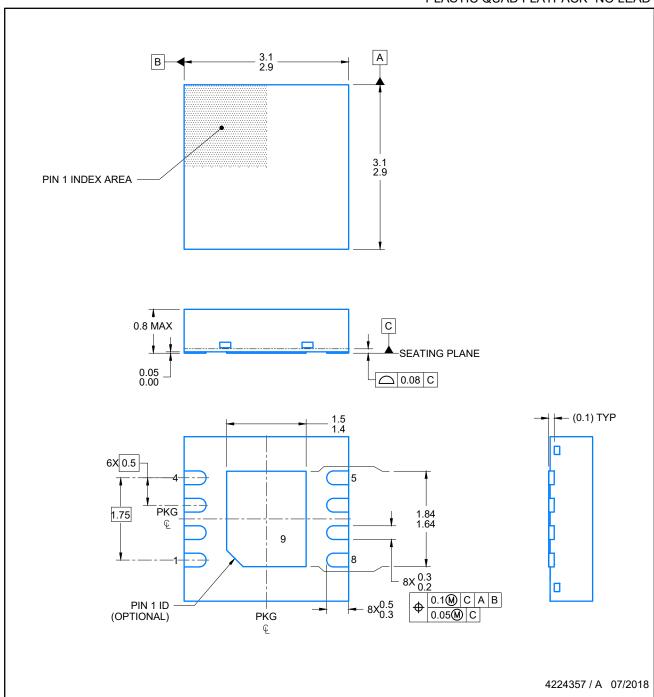

PLASTIC QUAD FLATPACK- NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

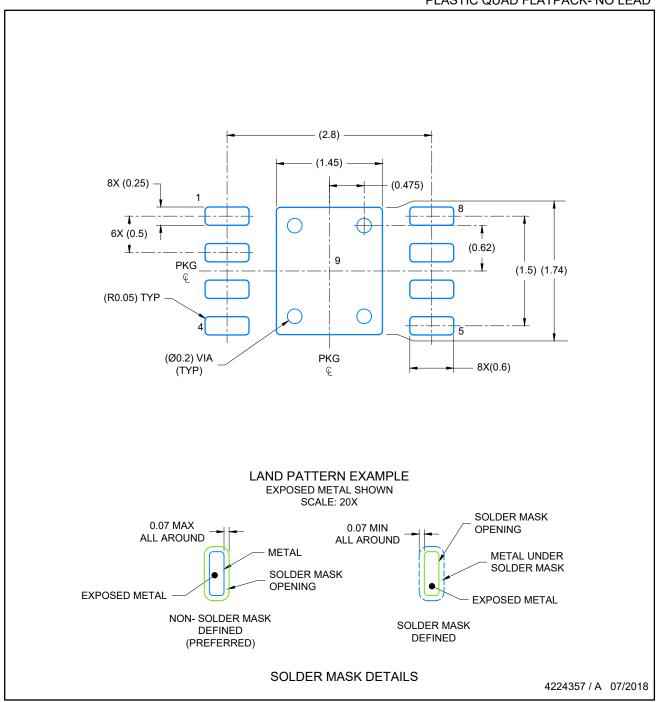

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

- 3. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271) .

- 4. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

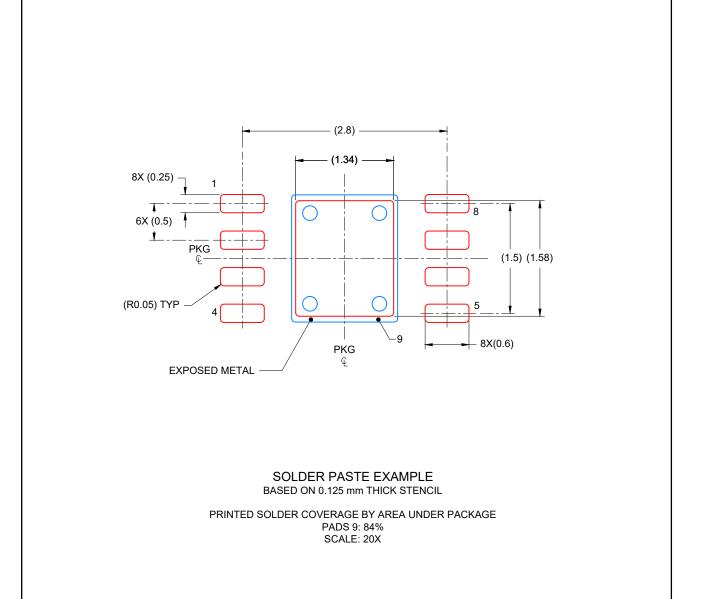

PLASTIC QUAD FLATPACK- NO LEAD

4224357 / A 07/2018

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations..

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated